How to develop your own microcircuit. I asked this question when I wanted to create my own processor. I went to google and found nothing good. The answers are mostly two։ "You won't make your own processor, because it's too difficult" and "Hammer and assemble a computer from components."

, . Verilog FPGA. , 3 , , FPGA. .

?

. .

. . . . . . , .

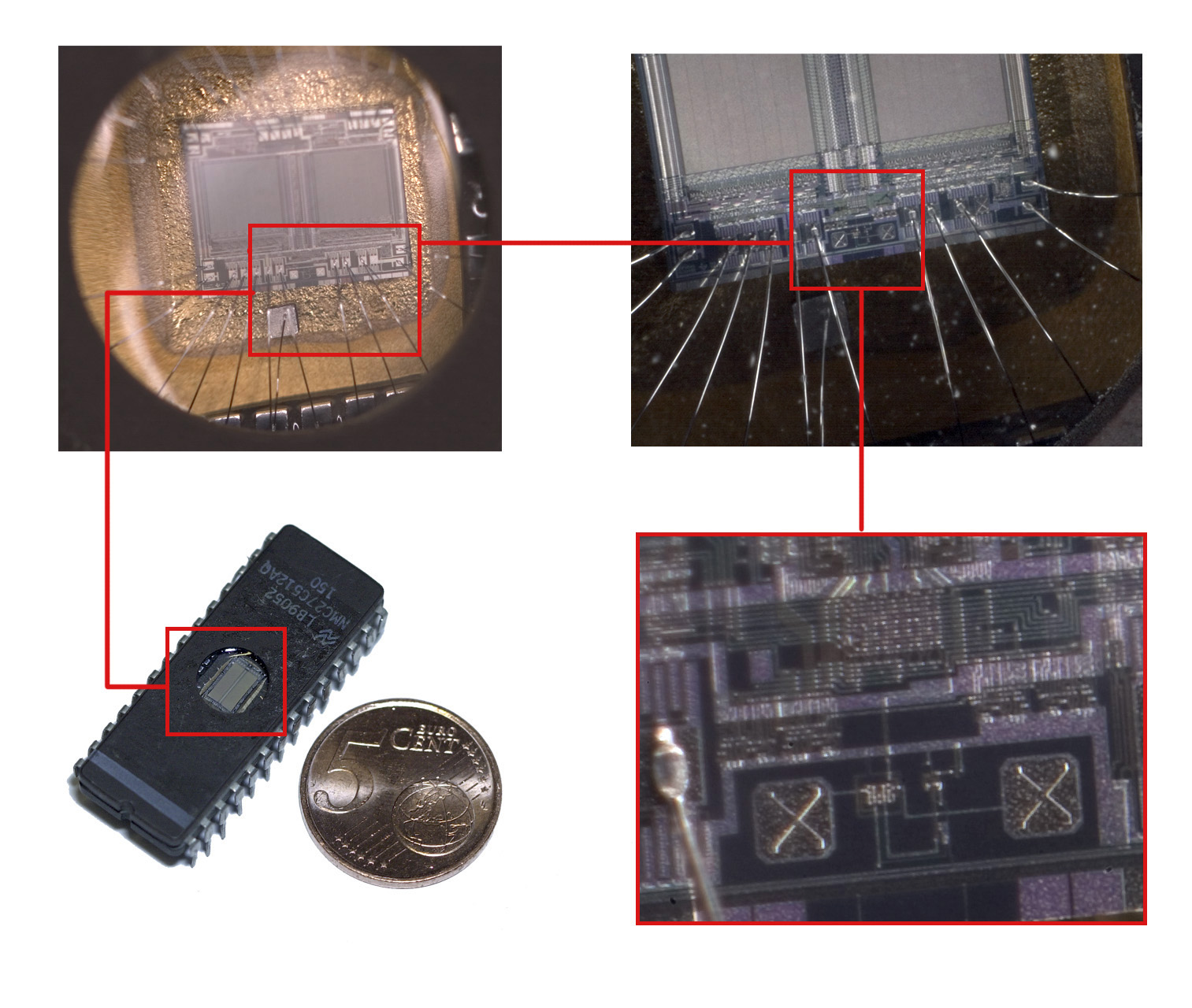

. . 130 .

, GDS-II , .

։ . 10000 , . Multi project wafer service [ https://en.wikipedia.org/wiki/Multi-project_wafer_service ].

GDS-II . , , .

GDS-II Process Development Kit

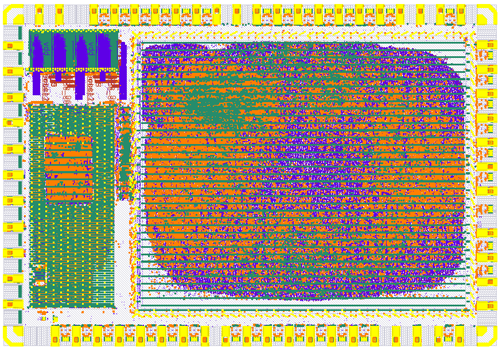

SHA3. SHA3 , Caravel Harness. SKY130 . Caravel Harness .

.

, .

SPICE.

. , , .

, GDS-II .

- , ,

-

Design Rule Check

, .

Primitive Extraction rules . GDS-II (netlist). netlist , netlist .

Layout versus Schematic check , GDS-II netlist. , .

Standard Cell Library. , . .

, .

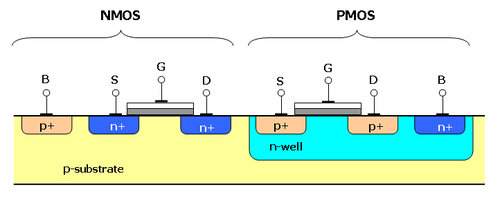

- - MOSFET. - NMOS PMOS.

. ։

։ . , N+ P Substrate. Vgs < Vth NMOS . Vgs >= Vth, Vds < Vgs - Vth . Vgs >= Vth Vds > Vgs - Vth . PMOS, NMOS , .

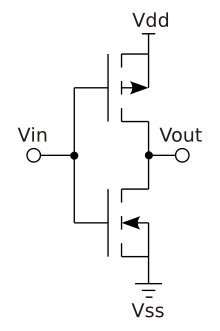

։ PMOS () NMOS ()

. Ubuntu ։ https://github.com/efabless/openlane#quick-start. ~/openlane_exp/

։ https://github.com/armleo/sky130_ubuntu_setup/blob/main/install_tools.sh

https://inst.eecs.berkeley.edu/~cs250/fa20/labs/lab1/

OpenLANE, . . skywater PDK + . .

Yosys. . ։ Claire Wolf. Verilog gate-level , . Design Compiler Synopsys

, gate-level GDS-II.

skywater-pdk. PDK skywater 130nm. , -

ngspice, spice. , HSPICE Synopsys.

xschem, . CustomCompiler Synopsys

klayout, GDS-II. CustomCompiler Synopsys

Magic, DRC, . . IC Validator Synopsys

Netgen, LVS . IC Validator Synopsys

OpenRAM. . Memory Compiler Synopsys. , - NDA. .

. , .

cd ~/openlane_exp/openlane

docker run -it --rm -v /home/armleo/openlane_exp/openlane:/openLANE_flow \

-v /home/armleo/openlane_exp/openlane/pdks:/home/armleo/openlane_exp/openlane/pdks \

-e PDK_ROOT=/home/armleo/openlane_exp/openlane/pdks \

-e PDKPATH=/home/armleo/openlane_exp/openlane/pdks/sky130A/libs.tech/magic \

-v /tmp/.X11-unix:/tmp/.X11-unix \

-v /home/armleo/openlane_exp:/home/armleo/openlane_exp \

-e DISPLAY=unix$DISPLAY \

-u 1000:1001 efabless/openlane:v0.12

klayout /home/armleo/openlane_exp/openlane/pdks/skywater-pdk/libraries/sky130_fd_sc_hd/latest/cells/inv/sky130_fd_sc_hd__inv_1.gd

X11 .

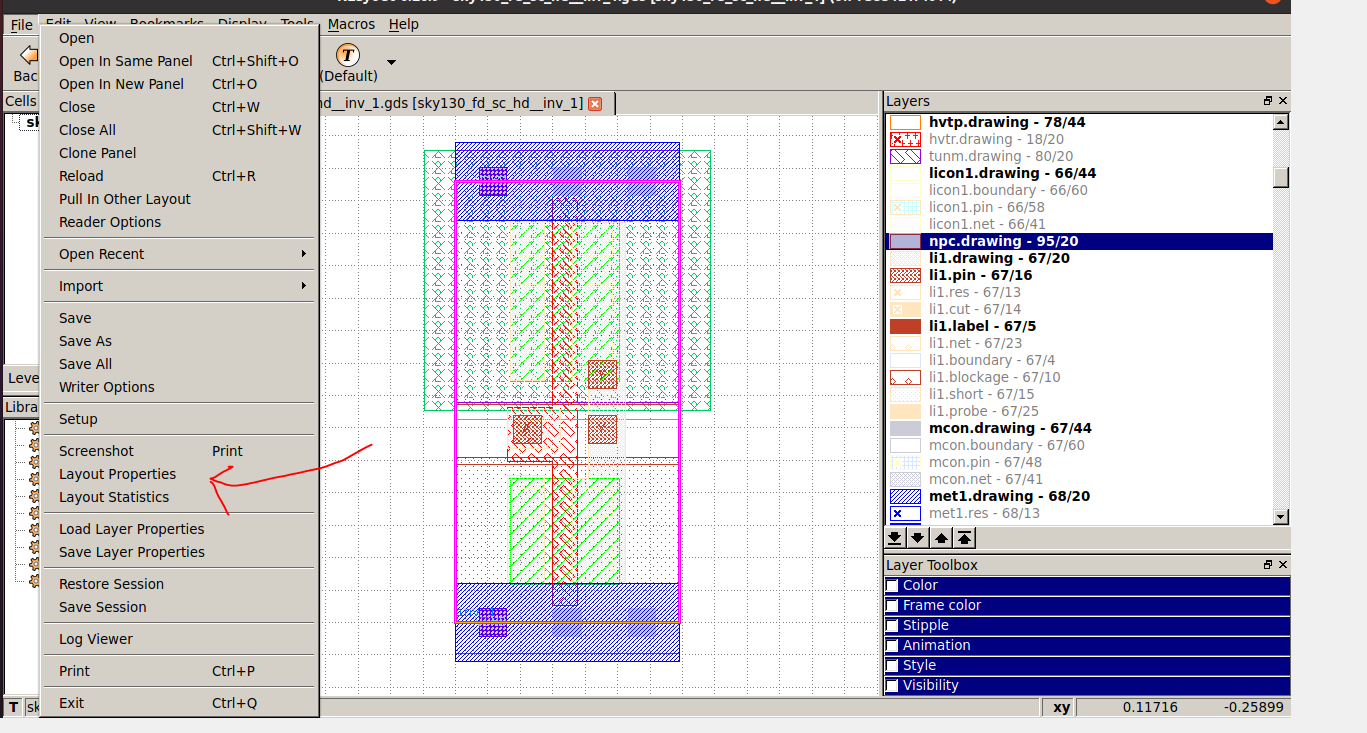

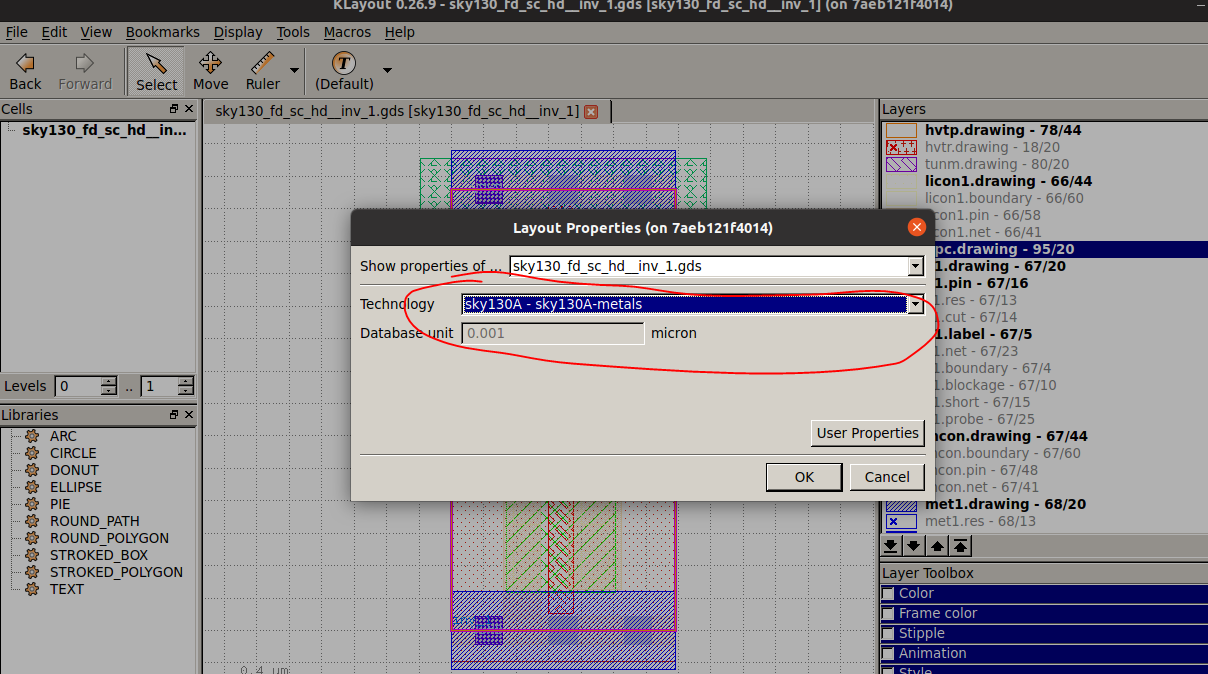

.

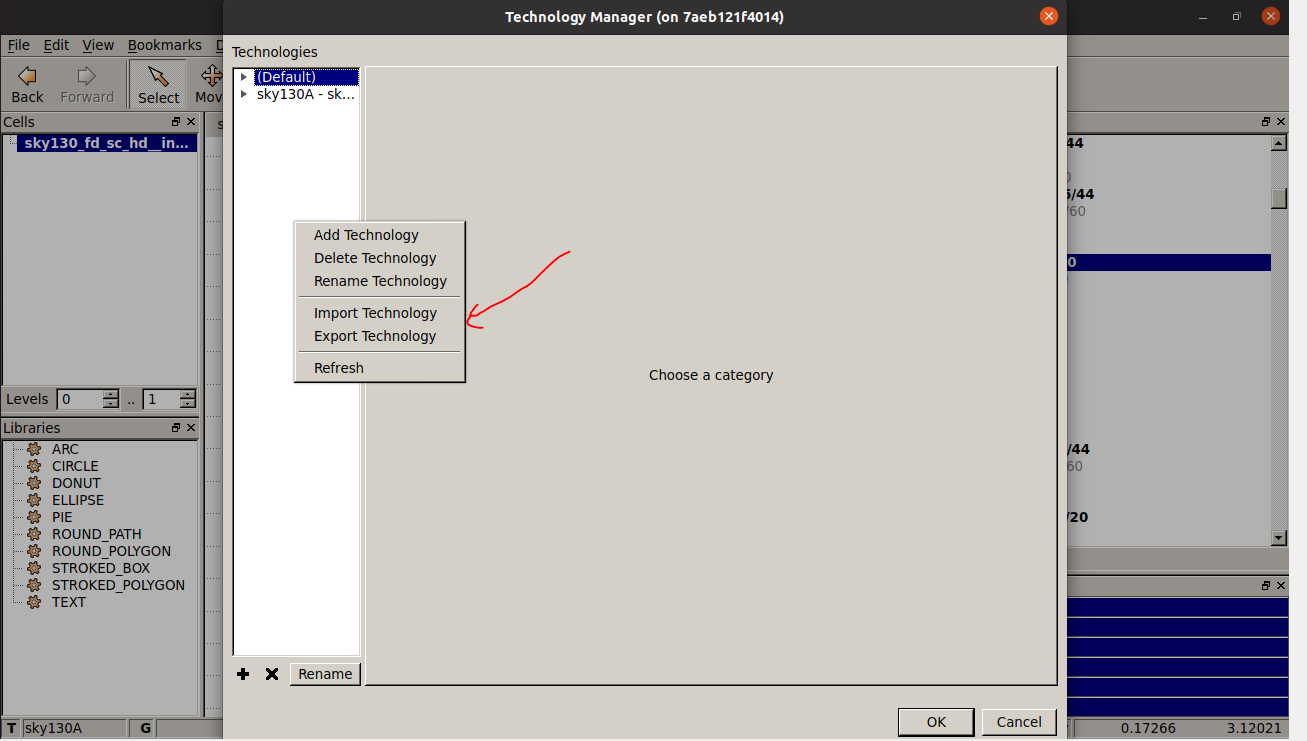

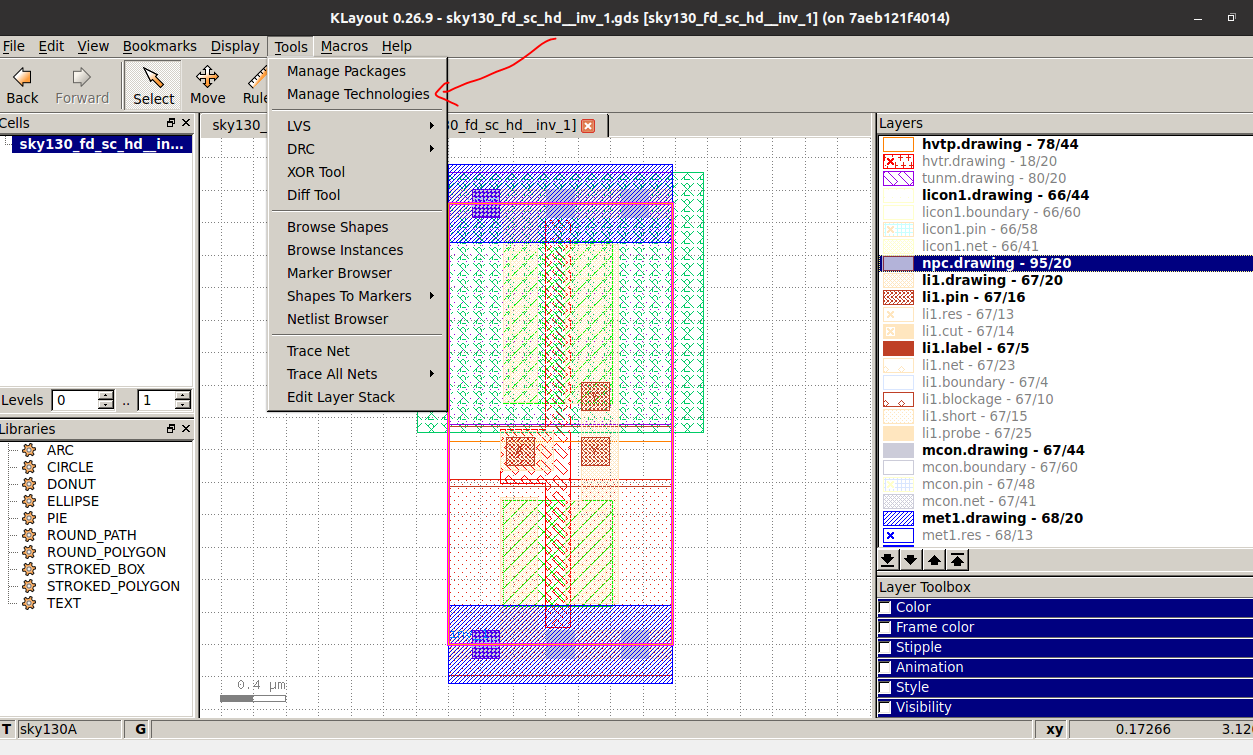

Manage Technologies

/home/armleo/openlane_exp/openlane/pdks/sky130A/libs.tech/klayout/sky130A.lyt

sky130A

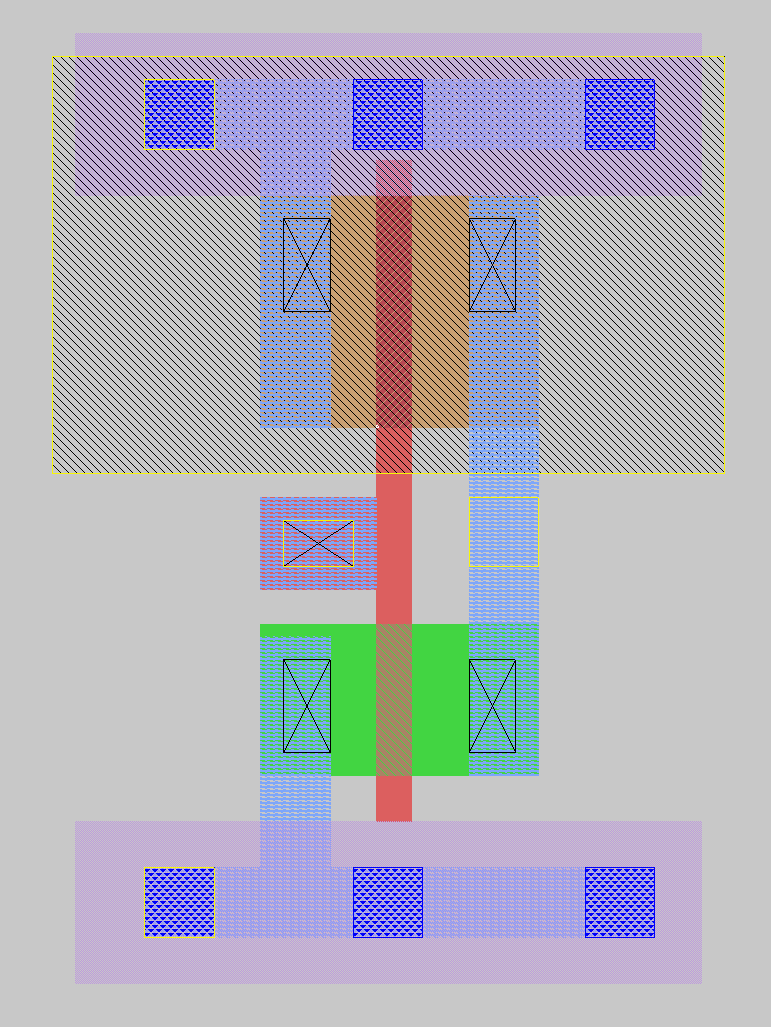

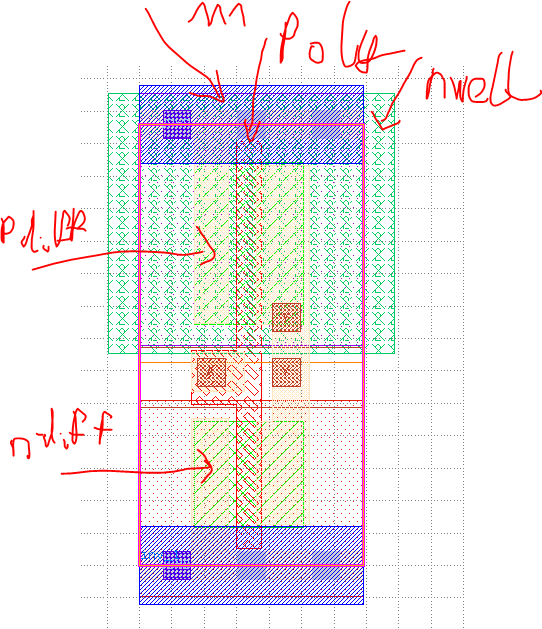

?

, ։D.

, . SOURCE BULK PMOS VDD . VGND , SOURCE BULK NMOS .

GATE A LI1.

Y LI1.

։

NMOS , , PMOS . . NMOS , , , PMOS .

NMOS , , PMOS VDD Y. NMOS , , . .

։

։

, 4 ։ DRAIN, SOURCE, GATE, BULK.

։

(NAND, NOR), LVS, DRC, PEX .

, (Sequential components) - Latch, Flip-flop

After that, we will analyze how to compile our Verilog in GDS.

Let's understand how to assemble our schema in Caravel