I have already talked about the newlyweds Vladislav and Elena Sharshin, who together with their colleague Andrey Papushin, Intel brought to California for the silver victory in the InnovateFPGA competition. Their interview is in the recently published "Digital Synthesis" lab . We are going to use this labnik at a seminar for schoolchildren and junior students, which will take place on September 15-17 at the ChipEXPO exhibition in Skolkovo . If you are going to repeat (or exceed) the achievement of the Sharshins and Papushin, or just become an FPGA or ASIC designer without leaving Santa Clara, then participating in a seminar, or even just looking at the initial instructions in this post, will help you get started.

Many of those registered for the seminar have already received FPGA boards (they are distributed by the educational department of RUSNANO) for passing the theoretical prerequisite . Now it would be very desirable if the seminar participants installed Intel FPGA Quartus (or, if someone doesn't like Intel / Altera, then Xilinx Vivado) in advance, and run at least a primitive test on it. Not even a blinking LED, but generally one XOR gate. If everyone does this in advance, then at the seminar we will discuss not trivial problems like “I don’t have a driver for USB Blaster”, but something more interesting, for example, what is asked in an interview for the position of RTL Logic Designer in NVidia, AMD, Apple and other companies.

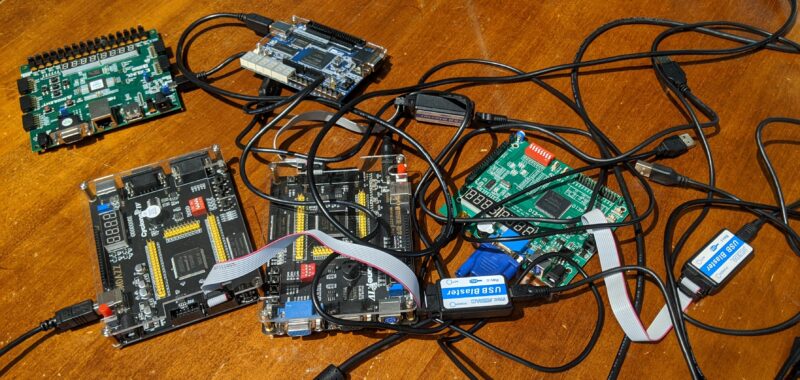

So, first of all, the seminar has an organization on github . You can clone the ce2020labs repository from here and use the files in the before directory to test your board, install Quartus or Vivado, drivers, and troubleshoot problems with the programmer. The directory contains files for seven boards: five boards with Intel FPGA (two variants OMDAZZ / rzrd, two variants ZEOWAA and Terasic DE10-Lite), and two boards with Xilinx (Basys3 and Nexys4).

If you don't want to use GitHub, you can simply download the zip from here . All of these files will work with both Windows and Linux versions of Quartus and Vivado.

To install Quartus, you can watch a detailed video from Sergei Ivants, Dean of the Faculty of Electronic and Information Technologies of the Chernihiv National Technological University:

Video:

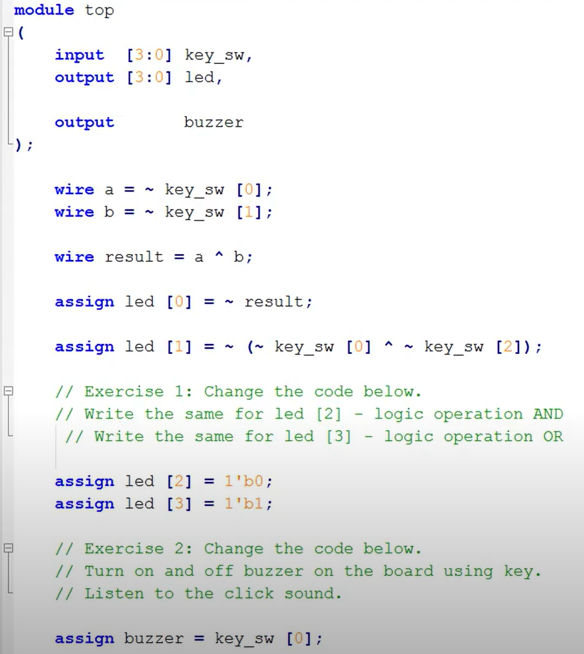

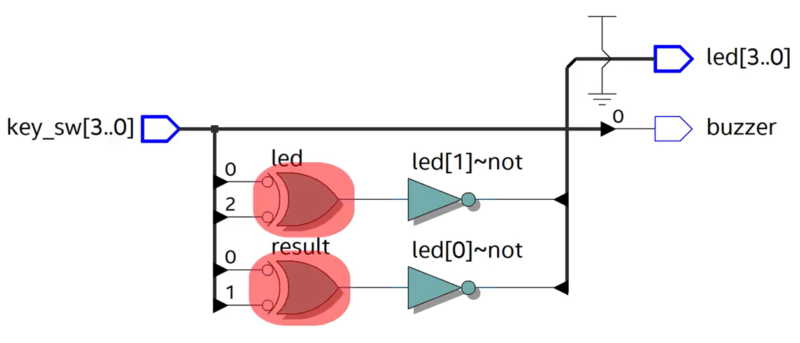

And a video on the synthesis of the simplest example from the description in the Verilog language:

With a detailed description of what's what:

The only problem is that this video does not cover the use of the programmer very well (and problems with its drivers). Therefore, you may find it useful to watch another video, also from Sergey, where he describes the use of USB Blaster after the schematic editor. Here it must be said that the schematic entry fell out of use by the designers of digital microelectronics in the early 1990s (everyone switched to design using the Verilog and VHDL hardware description languages), but Sergei nevertheless decided to show this purely so that a student starting to engage in digital design would immediately intuitively I realized that we are designing circuits, not writing programs, even though the code in verlog is similar to the code in a programming language.

Here's a video from the schematic entry, at the end of which the use of the programmer is described:

Before, during and after the seminar at ChipEXPO in Skolkovo, we will continue to upload various materials, but to watch everything (including, for example, a mini-lecture on how chip development teams in Silicon Valley are organized), it is better to register.