Do you want to know how to get a job designing spaceship electronics? I recently received an offer to interview for the position of FPGA designer for Blue Origin (see above). Personally, I don't need such a position (I already have an ASIC designer position in another company), but I noted that the technical requirements for applicants to Blue Origin exactly coincide with the content of the seminar for schoolchildren and junior students, which will be held on September 15-17 at the ChipEXPO exhibition in Skolkovo , with support from RUSNANO. Although, of course, at the seminar we will touch on Verilog and FPGA technologies only at the very initial level: basic concepts and simple, but already interesting examples. To get a job after that in Blue Origin, you still need several years of study and work.

Due to the coronavirus, the seminar will be remote, so not only schoolchildren and students of Moscow, but also all of Russia, Ukraine, Kazakhstan, California and other countries and regions will be able to take part. Lecturers and engineers from MIET, HSE MIEM, MIPT, Chernihiv Polytechnic University, Samara University, IVA Technologies and fpga-systems.ru will physically conduct lectures and remotely assist the participants .

To participate first, even before the seminar, you need to complete three parts of a theoretical course from RUSNANO, under the general title "How the creators of smart nanochips work": "From transistor to microcircuit", "Logical side of digital circuitry", "Physical side of digital circuitry". This course is essential so that you understand what you are doing during the workshop. Upon receiving a certificate of completion of the theoretical online course, you can go to the RUSNANO office in Moscow and receive a free fee for a practical seminar (if they stay, schoolchildren have priority). With this board you can work from home, before, during and after the Skolkovo seminar.

How to get paid, prepare for the seminar and what will be on it:

You can find instructions on how to get a fee on the STEMford website . STEMford is educational programs for schoolchildren from eNano , a subsidiary of the RUSNANO Foundation for Infrastructure Educational Programs. Here is their office to visit:

Before the lab, you will need to have Intel Quartus Prime Lite Edition installed on your computer. Instructions on how to do this are in the free fragment of the book "Digital Synthesis: A Practical Course" edited by A. Yu. Romanov, Yu. V. Panchul. DMK Press, 2020.

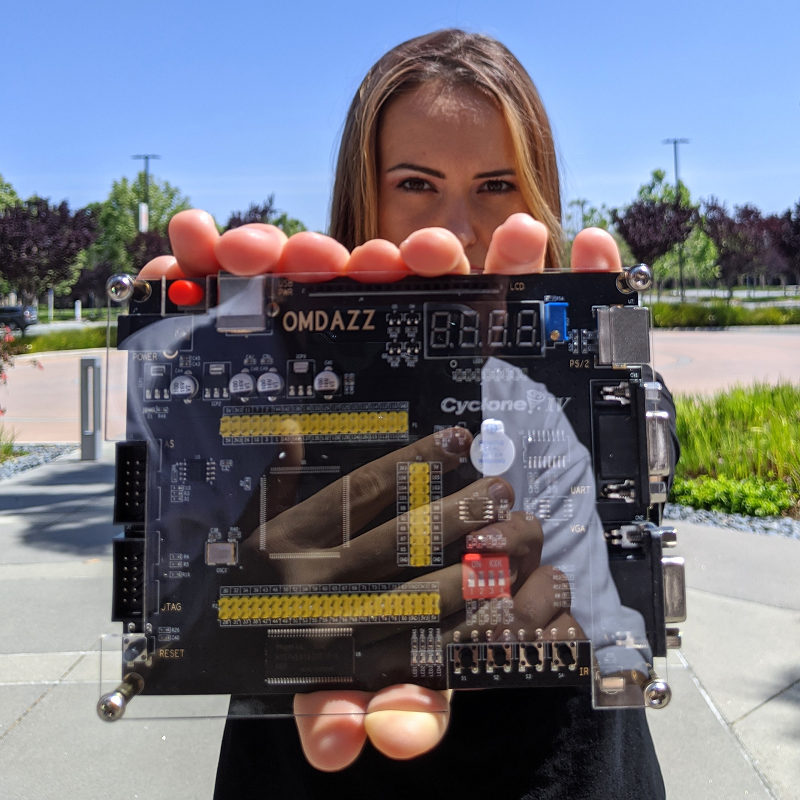

In general, "Digital Synthesis" is a useful book for a seminar, it describes exercises that will be presented with some variations at the seminar, although for example, instead of the schoolMIPS educational processor, a more modernschoolRISCV : At the end of the Digital Synthesis book, there is a rather amusing interview with a couple of newlyweds Vladislav and Elena Sharshin, which, together with their colleague Andrey Papushin, Intel brought to California for a silver victory in the InnovateFPGA competition: Here is one of the boards that will be used at the seminar. If there are not enough boards for you, or if you are not a student, you can order a board on AliExpress and in other places: 1 , 2 , 3 , 4 : What will happen at the seminar? Here are the parts of the program :

15 . .

: , « » ().

15.00. , .

15.15-15.30. -: Apple iPhone: .

, . , .

15.30-16.00. : Verilog. /FPGA Intel Quartus Prime Lite Edition. .

16.00-16.30.

///-, , c .

16.30-17.00. .

17.00-17.30. : , .

17.30-18.00. .

18.00-19.00. ZEOWAA OMDAZZ Intel FPGA Cyclone IV: : ( ). Terasic DE10-Lite Intel FPGA MAX10: : ( ).

19.00-21.00. , : , , ,

.

The first day is based on the experience of holding last year's seminar in Moscow, which is described in an article on Habré : The

second day is based on the experience of holding a summer school in Zelenograd last year and seminars in Samara:

16 . .

: , , , .

15.00-15.15. -: : , .

.

15.15-15.30. : VGA.

.

15.30-16.00. .

16.00-16.30. . Digilent Basys3 Xilinx FPGA Artix-7. .

, fpga-systems.ru.

16.30-17.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

17.00-17.30. : Linear Feedback Shift Registers (LFSR) . Verilog VHDL LFSR . LFSR VGA .

, .

17.30-18.00. ZEOWAA, OMDAZZ Terasic DE10-Lite.

.

18.00-19.00. .

.

18.00-21.00. , . .

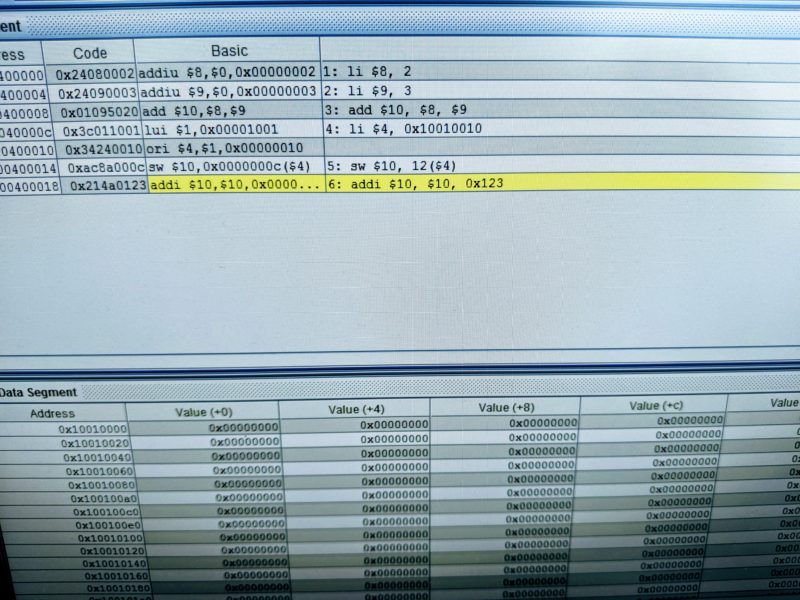

The third day will be based on the experience of educational program on processors from Stanislav Zhelnio and Alexander Romanov . Only before they developed and used the schoolMIPS learning processor, and now we will use schoolRISCV. The RISC-V architecture is very similar to MIPS and other RISC architectures (SPARC, ARM, POWER, etc.), but cleared of their crutches, which made sense on simple processors, but interfere with complex ones (register windows in SPARC, which are meaningless in software with a large stack; branch delay slots in MIPS up to Rev6, which are good on a simple static pipeline with sequential fetching of instructions, but turn into a headache in a dynamic pipeline, etc.).

Since in Russia there are at least three companies that design processors on the RISC-V architecture, and this is a good candidate for a future high-end Russian embedded and maybe even desktop and server processor, and since RISC-V confidently replaces MIPS as a working horses for architectural and microarchitectural experimentation in world universities, it is better to teach schoolchildren on it.

17 . .

— , ..., . .. (), « » ( ).

15.00-15.15. -: ENIAC , IBM/360 Cray-1 Intel, ARM RISC-V: , .

.

15.15-16.30. : . RISC-V .

, - .

16.30-17.30. : . schoolRISCV, . .

, IVA Technologies.

17.30-17.30. . .

.

17.30-18.00. Concluding Lecture: The Next Steps in Mastering Digital Circuit Design, and Applying This Knowledge to Design Embedded Systems and Artificial Intelligence Computing Accelerators.

Alexander Yurievich Romanov.

18.00-21.00. Additional exercises and individual student projects on changing the processor and integrating it with peripheral devices. With help from undergraduate and graduate students of microelectronics from participating universities.

Here is Stanislav Zhelnio teaching schoolchildren last summer in Zelenograd:

See you at a seminar at the virtual ChipEXPO in Skolkovo! We will try to hold a part of the event there and live, with the help of teachers from MIET, HSE MIEM and MIPT, but if the virus does not allow, we will conduct it in a distributed manner.